來源:智通財經

2023年9月13日,$蘋果(AAPL.US)$的秋季新品發佈會上,與iPhone 15 Pro系列一同登場的,還有全球首款3nm芯片A17 Pro,其依舊出自蘋果的老朋友臺積電之手。

在這款芯片發佈前,大家都對它寄予了厚望,與4nm這樣的小節點相比,3nm是繼5nm後又一次重要的工藝迭代,回顧過往歷史,每次工藝的大升級,都會帶來芯片性能的又一次大幅度提升,而3nm本該也是如此。

但意外偏偏發生了,這顆本應強大的A17 Pro芯片提升幅度並沒有大家想象中那麼大,反而iPhone 15 Pro的發熱問題,讓蘋果變成了“火龍果”。

那麼,發熱發燙這個鍋,是不是要讓$台積電(TSM.US)$來背呢?

神仙難救的散熱

很快就有人爲台積電撐腰了,天風國際分析師郭明錤發文,針對目前蘋果 iPhone 15 Pro 手機過熱問題進行了解讀,並表示“與台積電 3nm 製程無關”。

郭明錤稱,iPhone 15 Pro 系列的過熱問題,與台積電的 3nm 製程無關,主要很可能是爲了讓重量更輕,因此對散熱系統設計作出了妥協,像是散熱面積較小、採用鈦合金影響散熱效果等。

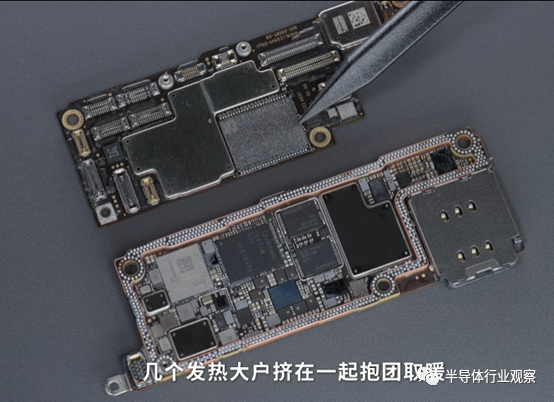

當然,這話說得確實挑不出毛病,根據目前的拆解來看,iPhone 15 Pro依舊採用的雙層主板,背部是ROM芯片,面前的是基帶芯片,都是發熱量較大的幾顆芯片,把它們放到一起,無異於讓A17 Pro待在篝火旁邊,負載一大,火勢就會變大,不僅處理器降頻運行,用戶也會很快就會感受到手機發熱。

外加蘋果在這次發佈會上吹了很久的鈦合金邊框,實際上還變相加劇了iPhone散熱差的毛病,鈦的導熱係數λ=15.24W/(m.K),約爲鎳的1/4,鐵的1/5,鋁的1/14,而各種鈦合金的導熱係數比純鈦的導熱係數還有再下降約50%,這也就是說iPhone 15 Pro雖然輕了,但是散熱反而不如iPhone 15的鋁合金邊框和iPhone 14 Pro的不鏽鋼邊框。

但是郭明錤這番話也並不全面,根據國內極客灣的測試,iPhone 15 Pro和iPhone 15 Pro Max的續航時間相較於上一代,反而出現了倒退,下降了幾十分鐘左右,在電池容量微增的基礎上,續航時間反而縮短,除了處理器本身性能調度原因外,問題恐怕還是出在了A17 Pro的本身的能效表現上了。

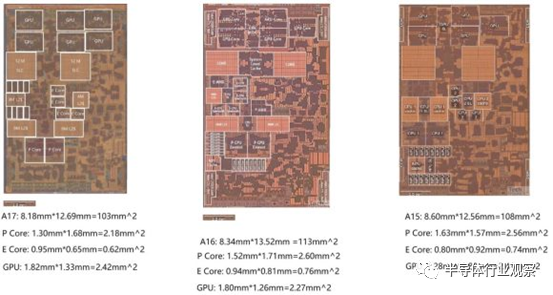

根據Techinsights的芯片拆解,與A16相比,A17 Pro 每顆性能核心和效率核心的面積減少了 20%,每個 GPU 核心的面積增加了 5%,整體 GPU 核心增加了 20%,且由於工藝製程的進步,A17 Pro芯片的整體面積略有縮小,但晶體管數量來到了新高,爲190億,對比上代的160億晶體管,增加了近20%,能夠完成如此大的升級,台積電3nm工藝功不可沒。

但根據蘋果官方的公告,A17 Pro的CPU整體性能只是比上一代提升了約10%,提升幅度達到20%的GPU又有很大程度上是因爲5核變6核,只有NPU提升幅度最大,算力從17TOPS升級到35TOPS,不難猜測它的實際規模變大了不少,外加新的USB 3控製器的加入,這些就是A17 Pro的主要升級點了,並未完成很多人預期裏的大幅度跨越。

當A17 Pro褪去了神話光環之際,台積電的3nm也備受質疑。

FinFET氣數已盡

爲什麼在4nm還順風順水的台積電,唯獨到了3nm時卻翻了車呢?

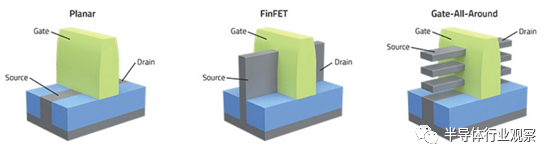

在5nm時,無論是台積電還是三星,都採用了FinFET(鰭式場效晶體管)的技術來控製流過晶體管的電流,這種技術能從「三面」來控製電子的通過(如下圖),若電子沒有被好好控製而亂跑,就會造成漏電,繼而使手機的溫度升高。

爲選擇更好的控製電流,兩家半導體巨頭都發展出從「四面」來控製電子通過的技術,稱作GAA(Gate-All-Around),進一步防止漏電發生。但在3nm這一節點,台積電選擇續使用FinFET工藝,直到2納米才轉換成GAA,三星則搶先在3納米時導入GAA,雖然目前還未大規模量產,但有望提供比FinFET更好的功耗與密度。

2011年,英特爾首度在Ivy Bridge 微架構處理器上應用22nm FinFET技術,2014年,台積電和三星首度在16/14nm工藝裏導入FinFET工藝,在隨後的幾年時間當中,FinFET成爲了衆多晶圓廠熱捧的技術,傳統平面工藝無法滿足先進製程的需求,摩爾定律再一次得到延續。

但沒過幾年,到了7nm製程以下,靜態漏電的問題越來越大,原本製程演進的功耗和性能紅利逐漸消失,FinFET無法滿足3nm及更先進製程的需求已成爲了大家的共識,何時導入GAA就成爲很多人關心的重點,英特爾和台積電選擇在3nm上繼續沿用FinFET,而處於競爭劣勢的三星下定決心,在3nm就引入GAA技術,力圖爭取到更多客戶。

在2020年8月的台積電技術研討會上,台積電表示,它已對其 FinFET 技術進行了重大更新,N3即3nm會使用 FinFET 的擴展和改進版本,性能增益高達 50%,功耗降低高達 30%,密度增益比 N5 提高 1.7 倍,不過這裏需要注意的是,這部分對比僅僅是初代N3與N5的對比,在N5經過多輪迭代升級到最新的N4之後,實際提升並沒有研討會上公佈的那麼美妙。

回過頭再來看GAA,台積電將其稱爲nanosheet FET,Intel稱其爲RibbonFET,這些技術本質都是一樣的,就是把FinFET的fin轉90°,然後把多個fin橫向疊起來,這些fin都穿過gate——或者說被gate完全環抱,所以叫做gate all around;另外每個翻轉過的fin都像是一片薄片(sheet),它們都是channel,因此也被稱爲nanosheet FET。

從結構上來看,GAAFET電晶體的gate與channel的接觸面積變大了,且每一面均有接觸,也就能夠實現相比FinFET更好的開關控製。而且對於FinFET而言,fin的寬度是個定值;但對GAAFET而言,sheet本身的寬度與有效通道寬度是靈活可變的。更寬的sheet自然能夠達成更高的驅動電流和性能,更窄的sheet則佔用更小的面積。

台積電沒在3nm用GAA的原因並不難理解,成本和技術。成本是新工廠新設施吃掉的資本投入,而技術呢,例如矽基通道中較低的空穴遷移率(hole mobility),導致pFET性能表現不佳。IBM在之前的IEDM上表示,這一問題的解決方法在於pFET可應用壓縮應力的鍺化矽(SiGe)通道材料:「pFET鍺化矽通道能夠實現40%的遷移率提升,相較矽基通道有10%的性能優勢,而且有更低的閾值電壓(Vt),負偏壓溫度不穩定性(NBTI)表現也有提升。」

當然GAA的好處並不明顯可能也是台積電的顧慮之一,三星此前談到了3nm GAA製程,其比4nm FinFET在頻率和功耗方面的優勢,如下圖所示,但圖中並沒有提供絕對值和相對值,其只是籠統地說,3nm GAA與4nm FinFET電晶體相比,在相同的有效通道寬度(Weff,fin/sheet的寬度× fin/sheet的個數)下,3nm GAA能夠達成更高的頻率;與此同時達成更低的功耗。

種種原因讓台積電打定主意,在2nm才會使用GAA,3nm成爲了最後一代FinFET,這也爲A17 Pro的翻車埋下了伏筆。

更要命的當然還是良率問題,根據 Hi Investment & Securities 的數據,三星的3 nm良率估計超過 60%,相比之下,台積電的 3 nm良率約爲 55%,新技術的良率幾乎與舊技術良率持平,讓人不由想起了幾個月前曝光的蘋果與台積電之間的“甜心交易”:蘋果向台積電下巨額 3nm 芯片訂單,但是要求不合格芯片成本均由台積電自己承擔,蘋果只需要爲良品芯片付費,有媒體表示,這樣下來,蘋果每年可節省數十億美元。

如果良率足夠高,蘋果也沒必要專程與台積電達成這項交易了,而台積電自2022年量產3nm至今,良率仍然沒有到達蘋果的底線,如今在能耗表現上也不理想,接下來能否說服更多客戶接受這樣一個價格再次上漲的工藝,或許才是台積電在2024年需要解決的大問題。

3nm誰領風騷?

目前,台積電爲蘋果代工的依舊是N3B即第一代3nm工藝,該工藝的好處是晶體管密度大幅增加,即A17 Pro實現的190億晶體管,而明年登場的N3E,在晶體管密度上表現會稍遜一籌,但功耗控製方面更加理想,包括蘋果在內的的多家廠商都有意採用這項工藝,如果屆時台積電能大幅提升良率,相信上門的Fabless廠商依舊會絡繹不絕。

但三星早已拿著GAA的3nm虎視眈眈,一旦台積電犯下錯誤,原本屬於它的訂單就有可能流向老對手,而這樣的局面早在16nm和7nm時就上演過,如今3nm懸而未決,未嘗沒有再發生一次的可能性。

3nm,是台積電亟需跨過的一道小坎。

編輯/Jeffrey